- Delay-locked loop

-

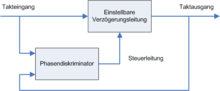

In electronics, a delay-locked loop (DLL) is a digital circuit similar to a phase-locked loop (PLL), with the main difference being the absence of an internal voltage-controlled oscillator. A DLL can be used to change the phase of a clock signal (a signal with a periodic waveform), usually to enhance the clock rise-to-data output valid timing characteristics of integrated circuits (such as DRAM devices). DLLs can also be used for clock recovery (CDR). From the outside, a DLL can be seen as a negative-delay gate placed in the clock path of a digital circuit.

Another way to view the difference between a DLL and a PLL is that a DLL is a first order loop and a PLL is a second order loop. A DLL compares the phase of one of its outputs to the input clock to generate an error signal which is then integrated and fed back as the control to all of the delay elements. The integration allows the error to go to zero while keeping the control signal, and thus the delays, where they need to be for phase lock. Since the control signal directly impacts the phase this is all that is required. A PLL compares the phase of its oscillator with the incoming signal to generate an error signal which is then integrated to create a control signal for the voltage-controlled oscillator. The control signal impacts the frequency of the oscillator, and phase is the integral of frequency, so a second integration is unavoidably performed by the oscillator itself. A first order feedback system is significantly easier to stabilize than a second order feedback system, which is a major advantage of DLLs.

The main component of a DLL is a delay chain composed of many delay gates connected front-to-back. The input of the chain (and thus of the DLL) is connected to the clock that is to be negatively delayed. A multiplexer is connected to each stage of the delay chain; the selector of this multiplexer is automatically updated by a control circuit to produce the negative delay effect. The output of the DLL is the resulting, negatively delayed clock signal.

The phase shift can be specified either in absolute terms (in delay chain gate units), or as a proportion of the clock period, or both.

Compared to phase-locked loops, delay-locked loops are a relatively recent innovation, first found in Dr. Combes' work[1] in the early 1990s[2], then popularized by Xilinx in their Virtex family of FPGA products.[3]

See also

- Phase-locked loop (PLL)

- Digital Clock Manager (DCM)

- Clock signal

References

- ^ Combes, M (1994-12-15). "Un générateur paramétrable de multiplieur de fréquence utilisant des techniques numériques". http://scholar.google.com/scholar?q=%22Un+g%C3%A9n%C3%A9rateur+param%C3%A9trable+de+multiplieur+de+fr%C3%A9quence+utilisant+des+techniques+num%C3%A9riques%22.

- ^ Combes, M (1995-09-19). "A Portable Clock Multiplier Generator Using Digital CMOS standard cells". http://ieeexplore.ieee.org/xpl/freeabs_all.jsp?tp=&arnumber=508209&isnumber=11008.

- ^ Kirk, Bob (2001-03-28). "Clock Management with PLLs and DLLs". EETimes.com. http://www.eetimes.com/isd/cover_story/OEG20010328S0051. Retrieved 2006-11-11.

The Delay Lock Loop has been derived by J.J. Spilker, JR. and D.T. Magill, "The delay-lock discriminator--an optimum tracking device," Proc. IRE, vol.49, pp. 1403-1416, September 1961.

Categories:- Oscillators

- Gate arrays

- Integrated circuits

- Digital electronics

- Electronic design

Wikimedia Foundation. 2010.